[TOC]

[TOC]

| doctor 医生 | good-looking 就好看的 | easygoing 随和的 |

|---|---|---|

| surgeon 外科医生 | attractive 有吸引力的 | open-minded 开明的 |

| actor/actress 女演员 | charming 迷人的 | caring 有爱心的 |

| archiect 建筑师 | gorgeous 漂亮的形容女生 | reliable 可靠的 |

| interior designer 室内设计师 | handsome 英俊的 | generous 慷慨的 |

| accountant 会计 | dashing 帅气的 | humorous幽默的 |

| lawyer 律师 | thick eyebrows 浓眉 | enthusiasm热情的 |

| sportsperson 运动员 | bright (男)/twinkling(女)eyes 明亮的眼睛 |

compassion同情心 |

| human resource manager 人力资源管理 | a sharp nose 坚挺的鼻子 | |

| sales represent 销售代表 | a smiling face 微笑的脸 | |

| 工作内容 | 工作技能 | 工作感受 |

| work in 在某个行业工作 | enhance interpersonal and communication skills 提高人际交往能例 |

give me a strong sense of achievement 给我强烈的成就感 |

| be responsible for be charge of 负责工作内容 |

achieve ones full potential 充分发挥潜能 |

Keep a work-life balance 工作与生活平衡 |

| my job mainly involves 我的工作主要包括(工作内容) |

a positive work environment that fosters teamwork 培养团队合作的积极工作环境 |

|

| work long hours for low pay | ||

| work under enormous stress 巨大的工作压力 |

||

| work around the clock 不停的工作 |

||

| 表示喜欢的句子 | 表示不喜欢的句子 | |

| i am pretty keen on i am really into i am quite a fun of i am crazy about i am fulled with joy when i am addicted to |

i am not so keen on … i am not really a fan of i really cant stand ….is driving me up the wall …is getting on my nerves |

原出处链接:开关电源的控制环截止频率和开关频率有什么关系

假设一个电力电子变换器开关频率为100k,调制波频率为10k,那么经过PWM环节得到占空比,状态空间平均法认为得到的占空比也是一个10k的交流信号(如图5所示的红线),即PWM环节等效为一个比例环节。

但实际上不完全是这样的,对占空比做傅里叶分析,可以知道占空比中除了10k的分量外,还有90K,110K,190K……的分量,那么状态空间平均法的准确度就依赖于这些非基波分量的抑制程度,显然,带宽越低,对这些非基波频率的分量抑制能力越强,状态空间平均法得到的模型就越准确。这是电力电子变换器环路截止频率为开关频率的1/5~1/10的重要原因之一,当环路截止频率超过开关频率的1/5以后,用状态空间平均法得出的模型就和实际模型差距比较大了。

[TOC]

而PCI9054的本地总线端的主要管脚信号定义如下表所示。这些管脚是连接到本地逻辑控制电路部分的,并由本地逻辑控制电路部分实现接口时序控制。

本组信号引脚主要用于PCI9054与Local端的连接,主要信号包括LA[31:2]、LD[3 1:0]、LHOLD、LHOLDA、ADS#、LCLK、LBE[3:0]#、LW/R#、READY#、WAIT#、BLAST#等。

| 引脚 | 定义 |

|---|---|

| CCS# | 配置寄存器片选。低电平有效时,选中的是PCI9054的内部寄存器,Local端可以通过此方法配置寄存器。 |

| LCLK: | Local端的时钟输入,是Local端处理器与PCI9054之间的同步信号,如果没有此信号,PCI插卡将不能启动。 |

| LINT# | :本地中断信号。作为输入时可以引起PCI 中断,作为输出时,可以通过改写中断寄存器INTCSR的内容来改变中断状态。 |

| LRESETo#: | Local端复位信号。当PC19054复位(RST#有效)时此信号有效,可以用来复位本地处理器。 |

| LA[31:2]: | 本地地址信号。代表物理地址的高30Bit,突发传输时可以自动增加表明一个连续的数据周期。 |

| LW/R#: | Local端的读写复用信号,低电平为读,高电平为写。 |

| READY#: | 输入/输出准备好信号,表示总线上数据有效或写数据完成,用以连接PCI9054等待状态产生器。 |

| ADS#: | 地址有效信号。表明LA[31:2]上的地址有效以及一个新的总线交易的开始,在第一个时钟周期内有效。 |

| BLAST#: | 突发结束。表明总线访问的最后一次传送,由本地总线主设备驱动。 |

| BTERM#: | 突发中止。用于中止一个突发传输并启动一个新的总线交易。 |

| MODE[1:0]: | 总线工作模式选择。 |

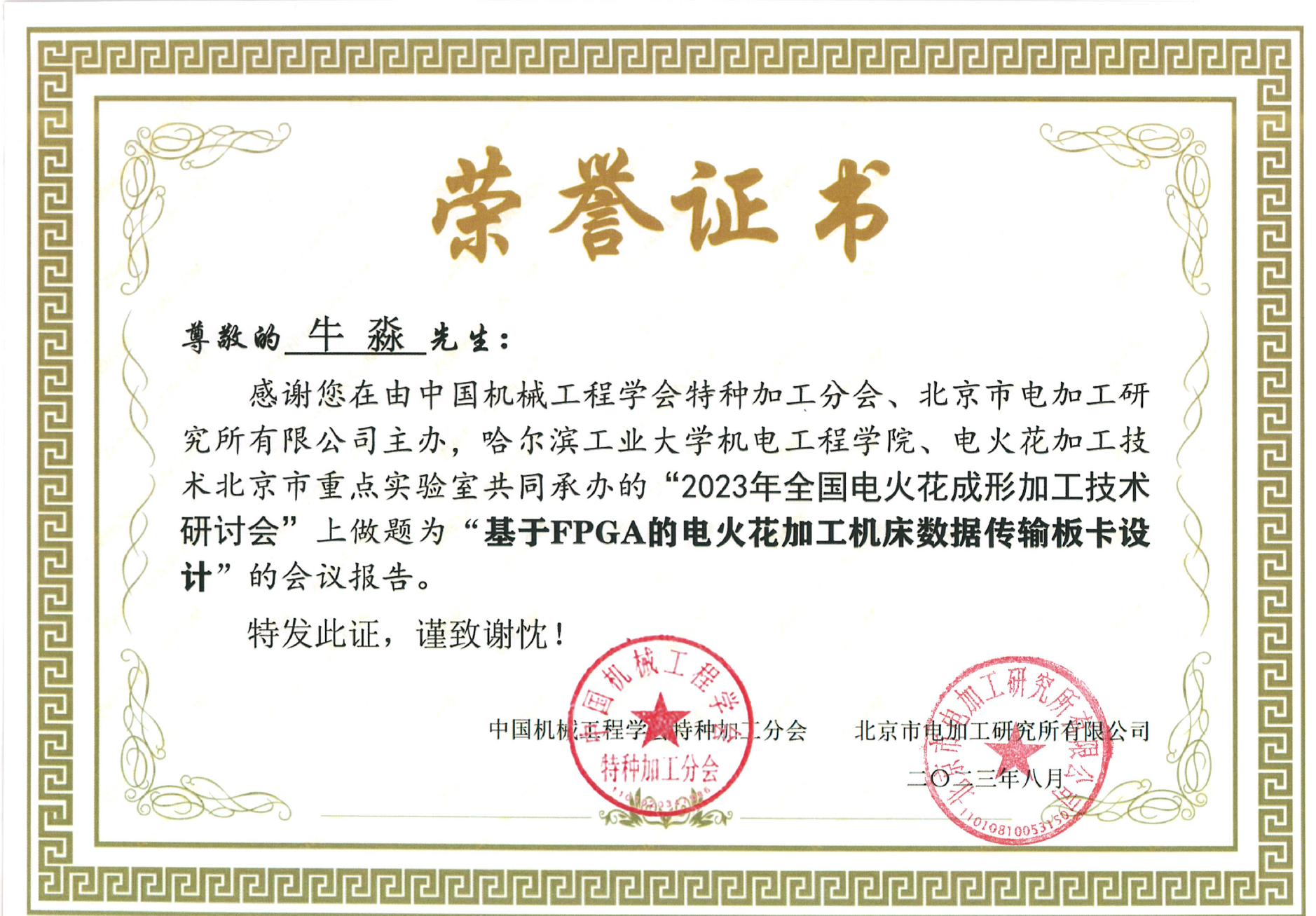

摘要:随着电火花加工的精细化发展,单个脉冲周期的能量越来越小、周期越来越短。单位时间内,因控制和状态检测而产生的数据量也越来越大,对数据传输速度的要求越来越快。并行执行的FPGA架构在数据处理上有着巨大的优势,基于EP4CE15F23C8设计了一种用于数据传输的FPGA数据传输NC板卡,详细介绍了设计方案和测试方案。数据板卡对下通过扩展IO实现了伺服电机控制、极间电压监测、人机交互、故障检测报警等功能,对上通过PCI总线完成了上位机通信控制、加工条件调节、状态检查传输等任务。并通过实验验证了以上功能;

关键词:电火花;FPGA;数据处理;数据传输;PCI总线

Abstract: With the development of electric discharge machining, the energy of a single pulse cycle is getting smaller and smaller, and the cycle is getting shorter and shorter. The amount of data generated due to control and status detection per unit time is also increasing, and the requirement for data transmission speed is getting faster and faster. The parallel execution FPGA architecture has great advantages in data processing. Based on EP4CE15F23C8, a FPGA data transmission NC board for data transmission is designed, and the design scheme and test scheme are introduced in detail. The data board realizes functions such as servo motor control, check of inter-electrode voltage, human-computer interaction, fault detection and alarm through the expansion of IO, and completes communication control of the host computer, adjustment of processing conditions, status inspection and transmission through the PCI bus on the upper side. Task. And the above functions are verified by experiments;

根据一篇专利来的

电火花加工电源的放电回路,包括工作电源、充电电源以及由电极和工件连接端子组成的放电支路,还包括分别与所述放电支路并联的消电离支路、负波吸收支路和增爆电容支路,所述放电支路的电极端连接所述工作电源的正输出端,工件连接端子端连接所述工作电源的负输出端,所述增爆电容支路由相瓦串联的容性单元和电容放电开关组成。所述电容放电开关和所述电容充电开关均为功率场效应晶体管或绝缘栅双极晶体管,所述电子开关为功率场效应晶体管或绝缘栅双极晶体管。该放电回路可极大地缩短申场建立时间,提高加工效率,同时改善加工表面质量,并且,还可提高消电离能力

| 组成部分 | 图中的那一部分 |

|---|---|

| 消电离支路 | 图中的2 |

| 负波吸收支路 | 图中的3 |

| 增爆电容支路 | 图中的4 |