环路补偿示例(例子)

为了说明使用Ⅲ型补偿方案的设计过程,以电压模式、CCM模式的Buck非隔离变换器为例。变换器相关规格如下

首先,需要定义PWM级的增益

接下来,将双极点的位置置于输出端滤波器的截止频率处

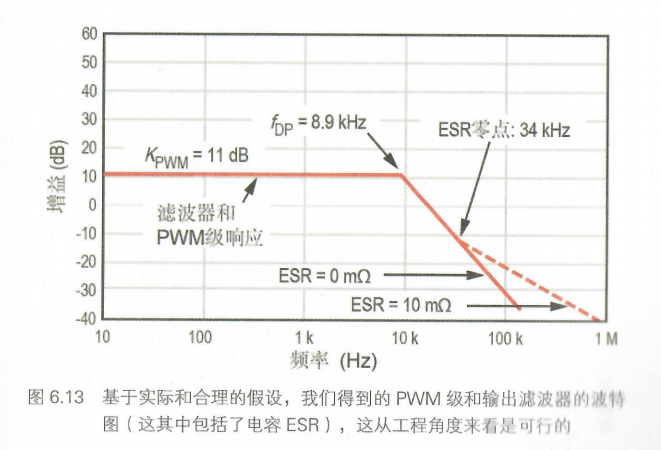

事实上,还需要考虑输出电容的等效串联电阻(ESR),另外还有许多寄生参数会影响元件的性能。例如,电感绕组中存在串联的直流电阻和并联电容,而输出电容也会包含一些小的串联电感,但是对于这一层面的分析,其中大部分通常可以忽略不计。

但是,电容的ESR是一个例外,因为我们很快就会看到,它足够大并可能影响我们感兴趣的频率范围内的性能。请注意,元器件制造商经常对这个数的定义并不明确,并且以非常保守的最大值作为指定值并写入规格书中同时 ESR具有一个负温度系数,所以应该考虑最低温度下的情况。

因此,我们通常必须进行假设,ESR可以具有从0到最大最坏情况值的任何值,在本例中可以高达10mΩ。因此,这个电容ESR会引入一个零点,从而在如下频率处增加滤波器的增益∶

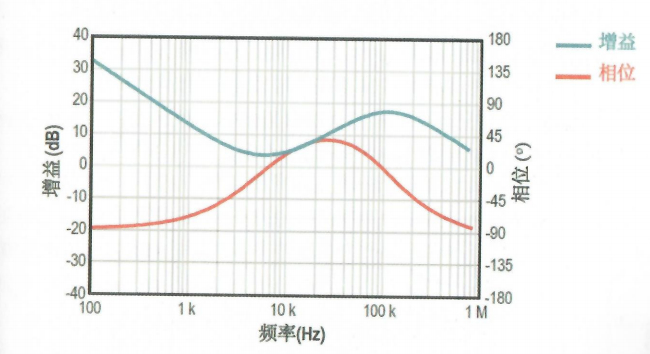

有了这些信息,综合PWM 和输出滤波器的增益,我们可以画出第一个波特图,如图 1所示。

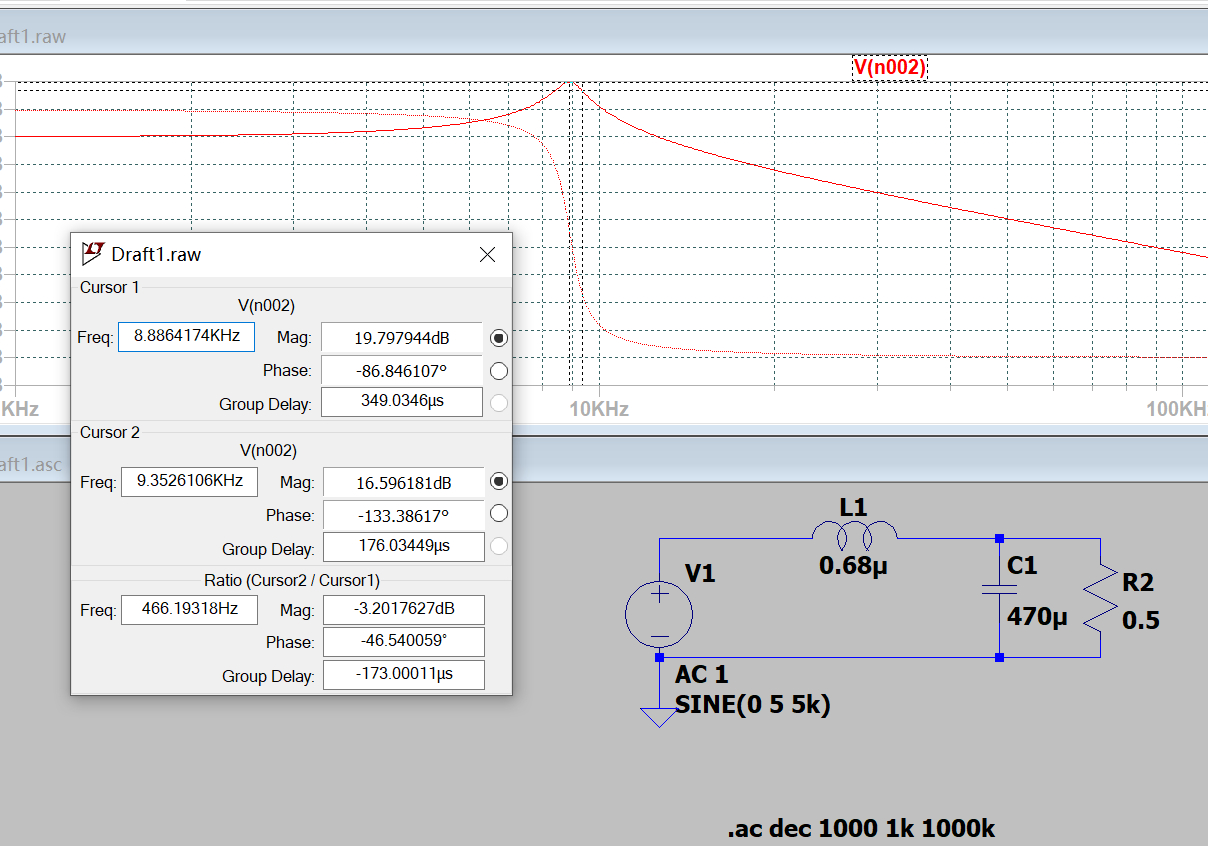

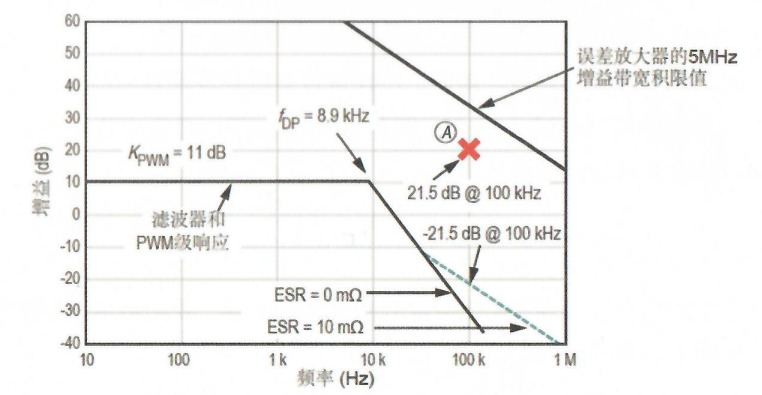

由于我们希望稳压器能够对快速变化的动态负载很好地进行响应。这需要很宽的带宽,所以采用Ⅲ型补偿电路。回到课本中的基本控制理论。个开关周期里采样5次,才能提供线性控制。这意味着控制环路的截止顺率/(增益低于0dB的频率)不应该高于开关频率的20%。对于这个例子,将设置$f_{C}=100kHz$,这是一个合理的数字,并留了一点的裕量。

截止频率,这是补偿曲线中的一个关键点,这也是一个很好的设计起点。在截止频率处,将补偿增益设定为等于输出滤波器的(负)增益,这样它们的增益和等于$0dB$,然后再转向其他频段的设计,如图2中的点A所示。

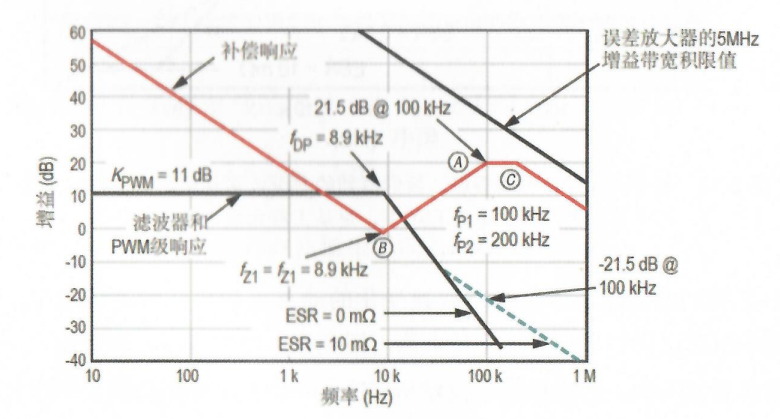

从这A点开始,我们可以得到一个下降的补偿增益,往左其斜率为-1下降,而在右侧较高频率时增益变得平坦。如果在这里放置一个极点,我们将其定义为$f_{p1}$。故进行Ⅲ型补偿,于是得到了图 3所示的整体补偿结果。

除了由极点$f_{p1}$定义的点A之外,在输出滤波器的两个极点所处的频率处(或在此附近),我们需要两个新的零点$f_{Z1}$和$f_{Z2}$在B点,两个零点的频率为$f_{DP}=8.9kHz$,随着频率从$f_{DP}$增加到$f_{C}$,补偿斜率从-1变为+1。在这个例子中,我们已经使得$f_{Z1}=f_{Z2}=8.9kHz$。

在$f_{C}$以上,补偿曲线的斜率是平坦的,但是在我们达到放大器的增益带宽限制之前,还需要一个额外的极点,因为通过补偿获得的增益无法大于放大器能够产生的增益。在这种情况下,我们在位置200kH处增加最后一个极点$f_{p2}$。

请注意,通过采用最大ESR来定义$f_{C}=100kHz$,ESR小于最大值时都将意味着在此频率下总增益将小于零。随着 ESR接近零,$f_{C}$将会降至接近 40 kHz。

现在已经定义了两个极点和两个零点的频率,但是在 DC 直流时还有第三个极点。这实际上是由初始-1斜率与放大器的开环增益相交的位置确定的,这个参数通常没有得到很好的定义。但是,已知道极点$f_{C}$增益和频率,

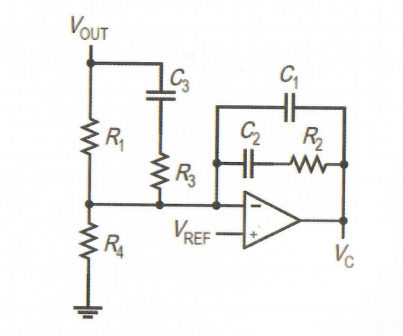

为了计算补偿电路中所有元件的值,最好从这里开始并在两个方向(此频率前和后)上进行设计。整个过程将使用图4的Ⅲ型补偿电路来进行描述。

零极点公式如下所示

现在知道了频率的位置,但是每个方程中仍然还有两个未知参数。综合上面四个方程,我们可以看到有些元件是相互耦合的(一个元件既在零点又在极点中都起作用),可以先随意假设一个值作为试探。对于图4所示,R-C 组合有许多种可能,而R-C并联支路在更高的频率下起作用,那意味着有∶

考虑到R4并不会影响AC的增益函数,所以在这里首先为它选择一个值,这是一个不错的出发点。设定$R_{4}=10KΩ$。

知道了$R_{1}$,可以计算出$C_{3}$∶

C3得到以后,可以得到R∶c

现在知道增益补偿的目标是$f_{c}$处为21.5dB(12),同样这个增益是由$R_{2}$和$R_{1}//R_{3}$、的比例决定的∶

$R_{2}$知道后,可以得到$C_{2}$∶

最终,可以计算出 C的值∶

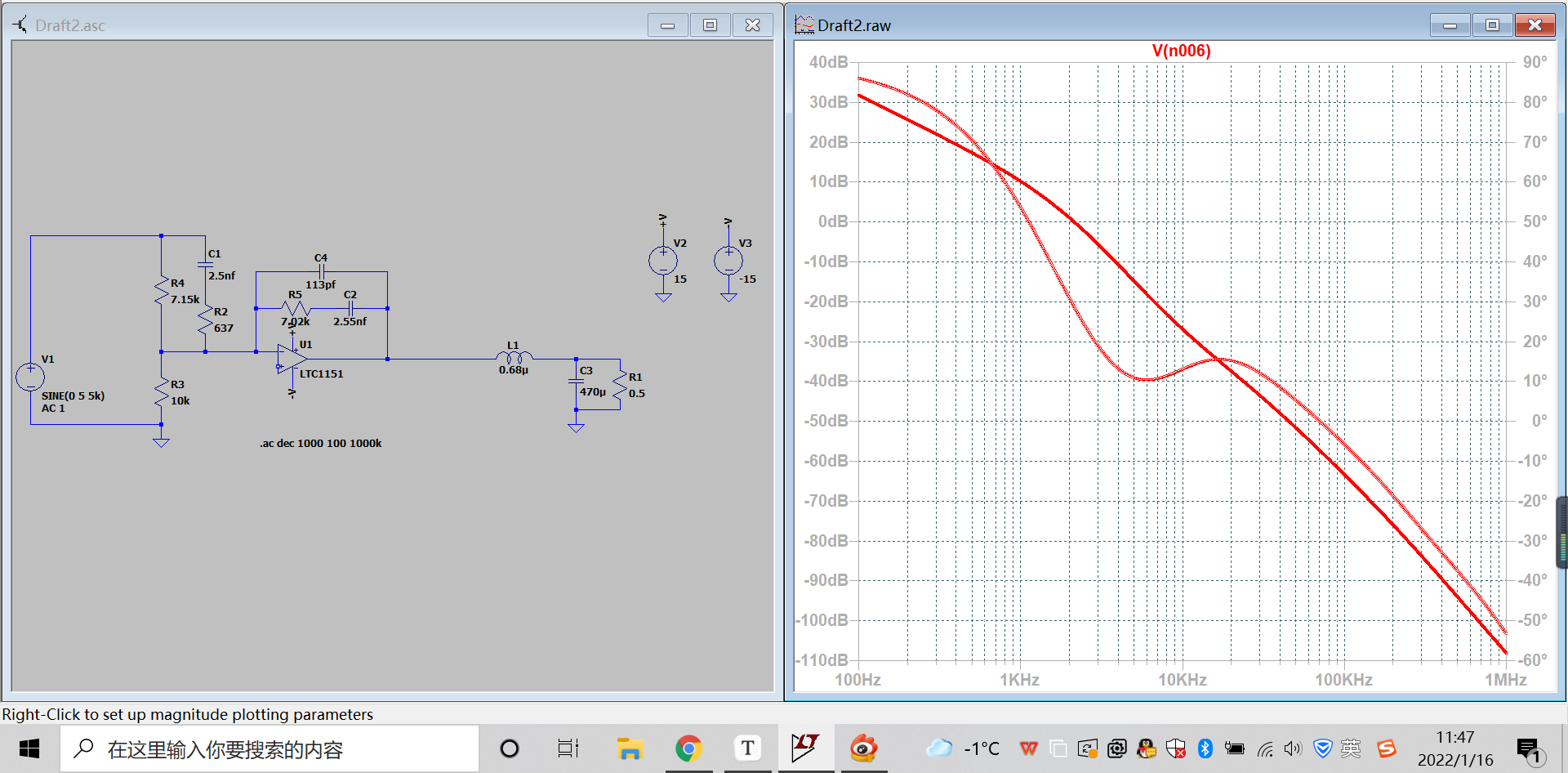

现在很方便可以利用电路仿真程序,绘制出补偿器的响应曲线,如图5.1与图5.2:

:

同样,增加PWM级和输出滤波器模块,我们可以得到了完整变换器的开环响应曲线。如图6所示。

。

补偿器计算增益曲线的峰值和谷值与我们设计时使用的图形化波特图中设置的值相比略有下降。这描述用直线近似法计算极零点产生的误差。在这种情况下,截止频率大约为40kHz,而不是设计目标中的100kHz。如有必要,可以通过对元件参数值小幅度修改来调整(二次迭代)。

实际变换器中使用元器件的值是由最接近的标准值组成的,测得的整体环路响应和计算值吻合得相当不错。